SamsPcbGuide Part 1: Evaluation of the inductance of elements of the printed circuit board topology

Foreword

In search of answers to questions arising from the design of printed circuit boards, I have studied a considerable amount of literature - both large monographs and individual technical articles. With the exception, perhaps, of several articles, this was English-language literature. I thought, why not formalize the accumulated experience in the form of practical guidance, which can be useful both for beginners and, I hope, for more experienced domestic developers. As a starting point, I was thinking of spreading valuable information, and with a margin of thought and contribution to the industry as a whole. This publication opens a whole series of articles in which, from a practical point of view, the main tasks arising during the development of printed circuit boards will be reviewed and key recommendations set out with a mandatory indication of their physical fundamentals and conditions of applicability. The last two factors are very important, as a separate recommendation may itself do more harm than good. In the conditions of accelerating the output of radioelectronic products to the market, microcircuit manufacturers strive to provide the consumer with ready-made solutions in the form of debugging and evaluation boards, instructions in the documentation, and also issue manuals containing a set of recommendations to developers with brief explanations (for example, [1] from Texas Instruments). These recommendations flow from manual to manual, losing their foundations and limits of applicability and as a result, as stated in one of the articles [2] on the website LearnEMC:

The worst printed circuit boards, as we have seen, were designed by engineers who tried to ensure that all items on the list of recommendations for improving the EMC of printed circuit boards.A number of recommendations contradict each other, and some continue to be used, despite the fact that they are outdated. That is why I urge the expert community to discuss, feedback, both positive and negative, for constructive criticism based on real-world experience in PCB design. With one common maximalist goal - to get to the bottom of the truth, to the basic practical principles.

Inductance and Electromagnetic Induction

The first publication is not accidentally devoted to inductance. Understanding the physical fundamentals of inductance is critically important, since the inductance (or rather, parasitic inductance) of the PCB layout is associated with many EMR and EMC problems, which will be discussed in subsequent articles of the cycle. The complexity of the question can be judged by fuzzy terminology, when a single term “inductance” refers to quantities, though related, but having completely different mathematical and physical meanings: inductance of case leads, inductance of a coil, parasitic inductance of an ESL capacitor, loop inductance, etc.

According to the classical definition [3], inductance is the coefficient of proportionality between the dc power in a thin closed conductive loop and the magnetic flux through this loop. The first thing to look out for is the inductance defined for a closed loop. The definition also refers to the full magnetic flux, let's deal with it. A moving electric charge generates a magnetic field, and a magnetic field around an electric current - a superposition (vector sum) of the magnetic fields of individual charges. For a visual image of magnetic fields, lines of force are used. The direction of the tangent to the line of force at each point coincides with the direction of the magnetic field vector at that point. For example, for a current in a long straight wire, the power lines are concentric circles, the plane of which is perpendicular to the wire, and the direction is determined by the well-known “right-hand rule” (Fig. 1). With the help of lines of force, it is possible to judge the relative strength of the magnetic field - it is the higher, the higher the density of lines of force (the number of lines per unit area perpendicular to them). Further, the magnetic field flux B is the surface integral of the magnetic field strength:

where surface S is determined by the current loop. Consequently, the flux of the magnetic field is proportional to the number of magnetic field lines through the surface S and the definition of inductance can be reduced to a more convenient from a practical point of view:

Inductance is proportional to the number of magnetic field lines that intersect the surface defined by the current loop, with a current of 1 A.

A change in the current leads to a proportional change in the strength of the magnetic field, which can be conventionally represented as a change in the number of lines of force around the conductor. Such an approach to understanding inductance, described by Eric Bogatin [4, 5], was subjected to well-argued criticism from an equally authoritative author, Clayton Paul [6, 7]. Indeed, the lines of force is an abstraction and no one determines inductance by counting their number (which is obviously infinite). However, such a visual representation simplifies the understanding of many laws related to the magnetic field. While theoretical physics seeks to search for a universal equation that describes all interactions, for practical purposes, we look for approximate analytical relations that have a low computational complexity. In practice, no one begins the analysis of the electrical circuit with the formulation of Maxwell's equations for its sections. Even despite the emergence of CAD, which removes the issue of computational complexity, the need for simplified relations is preserved, since they provide a qualitative understanding of the basic laws and allow you to perform the initial estimated engineering calculations.

One important note should be made: the inductance does not depend on the magnitude of the current and is determined by the configuration of the current lines in the conductor. Often, such a formulation speaks of the determining value of the conductor geometry, but such a formulation does not take into account the effect that the current distribution in the conductor is not always uniform - it is influenced by the current frequency (skin effect) and the proximity of other conductors to current. The simplest case for obtaining analytical relations is the uniform distribution of the current over the conductor cross section and all known analytical relations are obtained by taking into account this assumption. In practice, these effects have little effect on the value of inductance and the use of these formulas for calculating inductance provides sufficient accuracy for practical problems.

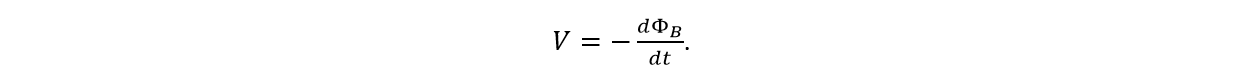

Consider a physical phenomenon associated with inductance, which determines its fundamental role in EMC and EMR. It is opened by Michael Faraday and is called electromagnetic induction. According to the law of the same name, when the flux of a magnetic field Φ B changes, an emf arises through a closed loop:

In terms of lines of force, this means (remember the conventions of this approach):

A change in the number of lines of force through a closed loop leads to the appearance of an emf voltage in it.

This change can be caused by any of the reasons: a change in the current in the conductor itself, a change in the current in the adjacent conductor, a change in the geometry of the circuit or its orientation in a magnetic field, finding the circuit in an alternating magnetic field, changing the distance to another circuit with current, etc. P.

Partial inductance is a handy tool.

Before proceeding to the formulas, we draw a distinction between different types of "inductances" and clarify the terminology (Fig. 2). If the magnetic flux is calculated through the circuit, caused only by the current in the circuit itself, then we speak about the own inductance of the circuit L (eng. Loop inductance, self-inductance). If the magnetic flux through the circuit, caused only by the current in another circuit, is taken into account, then this is the mutual inductance of the circuits M (eng. Loop mutual inductance). From a practical point of view, it is important to question what the inductive emf voltage is equal to in a particular part of the circuit of an electric circuit. But for this it is necessary to connect the value of inductance with this section, and the inductance of the circuit in this sense is indivisible. Therefore, a mathematical apparatus was developed for calculating the partial self-inductance of a section of an L P circuit (partial self-inductance) and a partial mutual inductance of two sections of one or different M P circuits (partial mutual inductance). They are calculated so that the magnetic field is taken into account, caused only by the current of this area, as if the rest of the circuit does not exist. Otherwise, it can be represented as follows - the rest of the circuit is replaced by infinitely long lead wires and the circuit, through which the magnetic flux is calculated, is defined as in

Knowing the values of the partial proper and mutual inductances of individual sections of the circuit, the value of the inductance of any combination of them, including the entire circuit, can be obtained:

here L i P is the own inductance of the i-th section, M ij P is the mutual inductance of the i-th and j-th sections, the sign of which is positive if the currents in the sections are co-directed and negative otherwise. Mutual inductance has the property of symmetry, that is, M ij P = M ji P , for areas perpendicular to each other, the mutual inductance is zero. If only the current of the considered component section is taken into account, then this formula gives its partial inductance, if the second sum takes into account the effect of the entire circuit, then the resulting value is the total inductance of the section (English total inductance, net inductance) (Fig. 3).

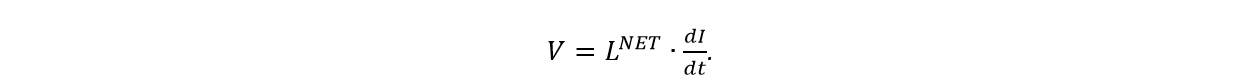

It is the total inductance that determines the voltage drop in the area when the current I in the circuit changes:

From the formula for the total inductance of the rectangular contour section L 1 NET in fig. 3 that this value is smaller, the greater the mutual inductance of this area with its opposite M 13 P. That is why the convergence of the signal path and the support layer is recommended as a measure of noise reduction in the support layer.

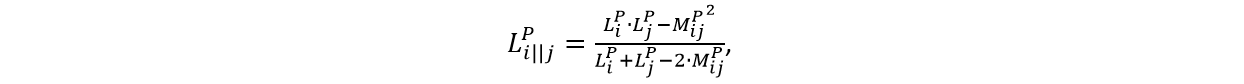

The partial inductance of the parallel connection of two sections is calculated by the formula:

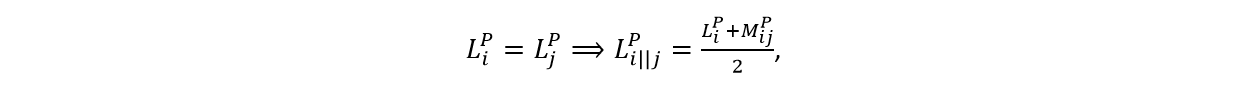

which is only in the case when the mutual inductance is negligibly small (considerably removed conductors) turns into a well-known formula for parallel connection of inductors. In the case of identical conductors (for example, two identical vias), the formula takes the form:

that is, the inductance is halved only for conductors, the distance between which is large enough to neglect their mutual inductance.

Calculation formulas

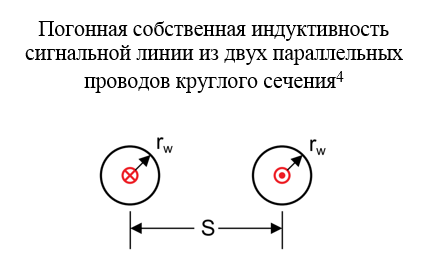

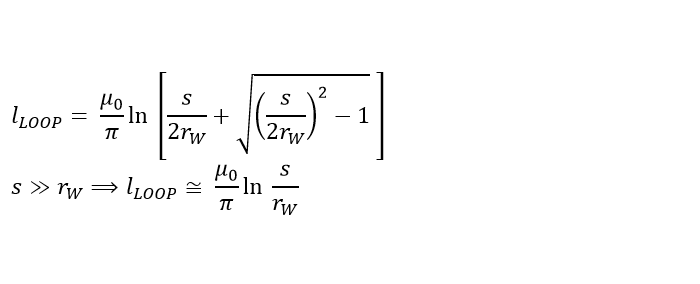

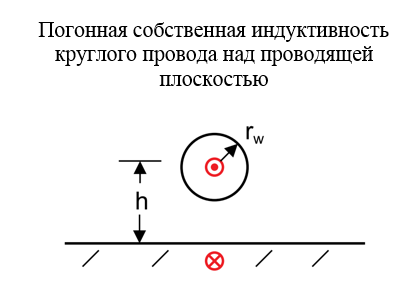

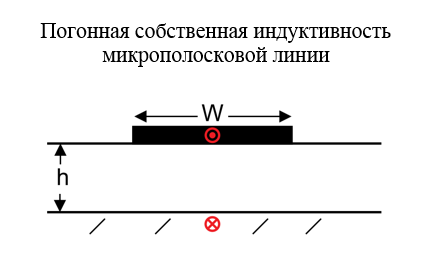

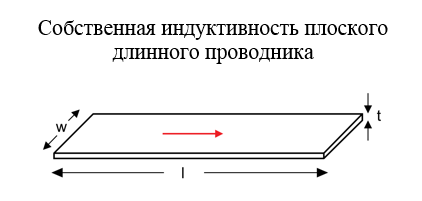

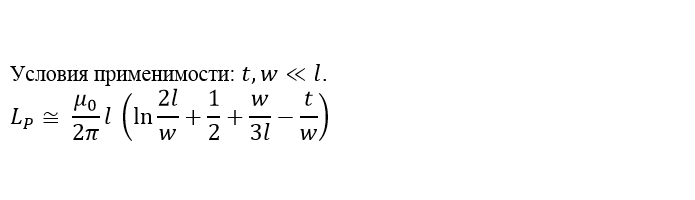

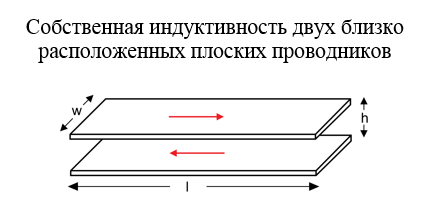

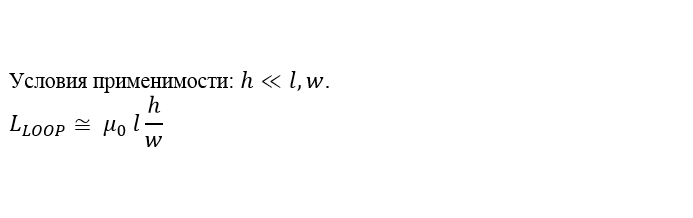

Table 1 on the schematic images of the arrow indicates the direction of the current, the distribution of which is uniform over the cross section. Since it is the current distribution that determines the inductance, it is important to relate the current distribution in the structure of the printed circuit board to the one specified in the table. Another condition for the applicability of the formulas, which must not be forgotten, is the requirement that the characteristic dimensions of the conductor l be small compared to the wavelength λ (at least l <λ / 10 ), since the current at all points of the conductor can be considered the same. By the way, exactly the same restriction is imposed on the applicability of the model of electrical circuits with lumped parameters.

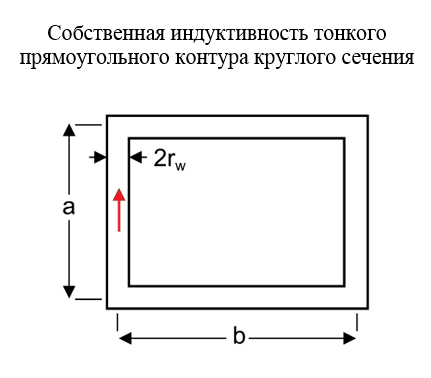

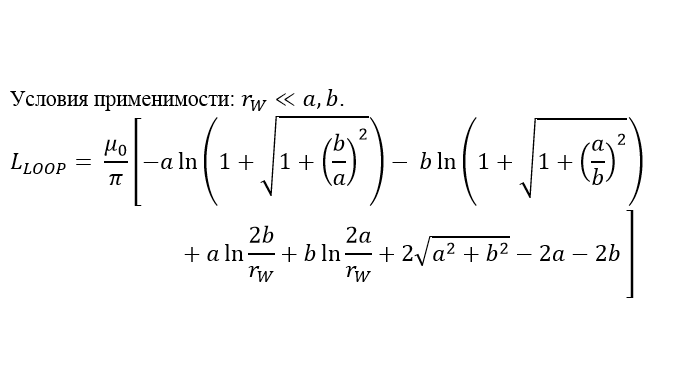

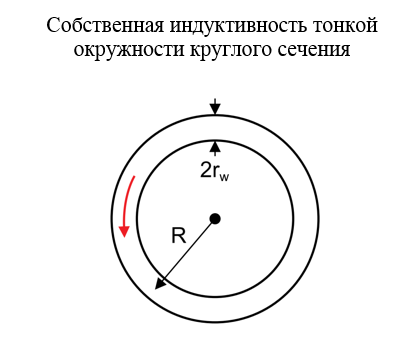

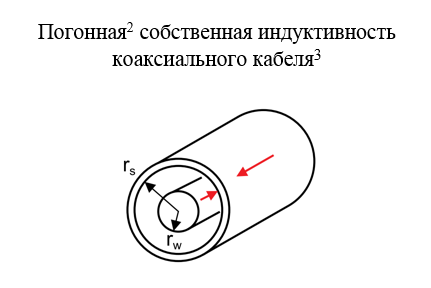

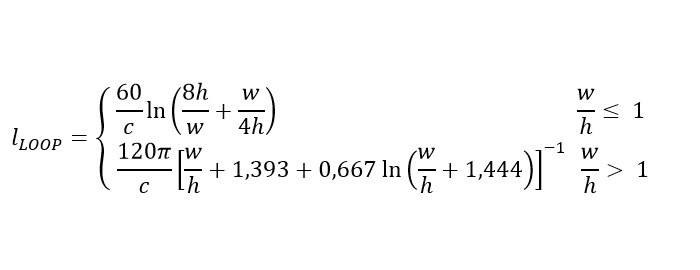

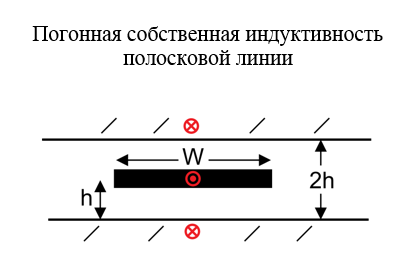

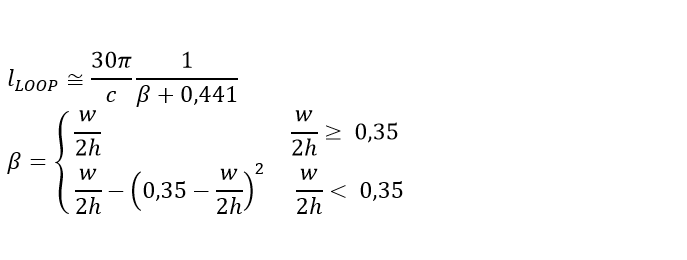

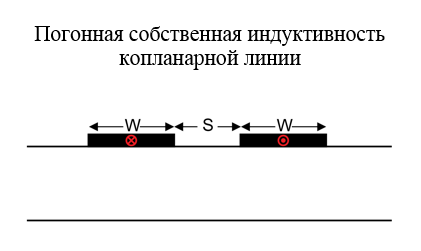

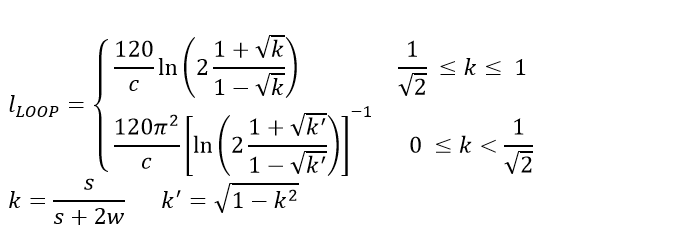

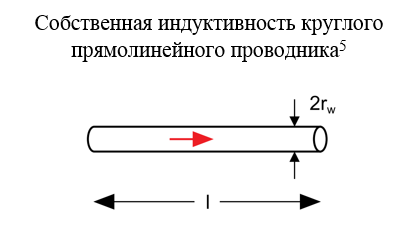

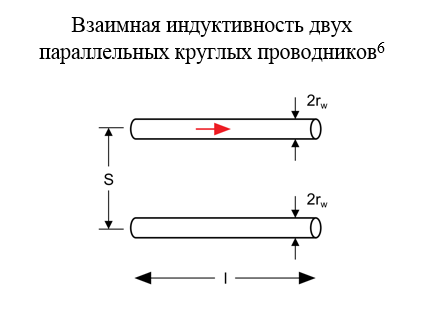

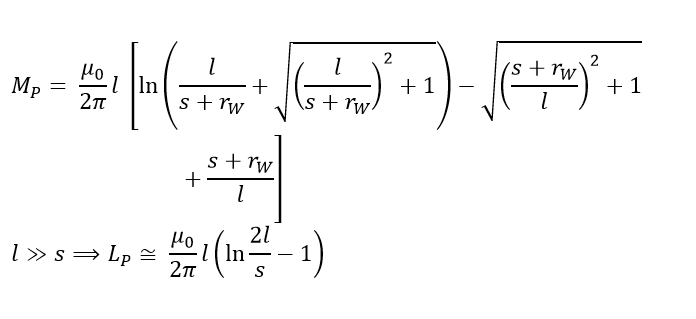

Table 1. Formulas for evaluating the inductance of elements of the topology of a printed circuit board 1 .

| Name and schematic | Formula |

|---|---|

|  |

|  |

|  |

|  |

|  |

|  |

|  |

|  |

|  |

|  |

|  |

|  |

|  |

Notes to table 1:

1. For a medium with relative magnetic permeability μ r = 1.

2. Calculated per unit length.

3. The formula is sometimes used to estimate the self-inductance of a vias between two continuous layers under the assumption that the return bias current is evenly distributed around the hole.

4. The formula can be used to estimate the inductance of a pair of vias (for example, connecting a blocking capacitor).

5. The formula can be used to estimate the self-inductance of a vias.

6. The formula can be used to estimate the mutual inductance of parallel vias.

7. Dimensions of continuous conductive layers should be large enough so as not to limit the current distribution between the vias.

Examples

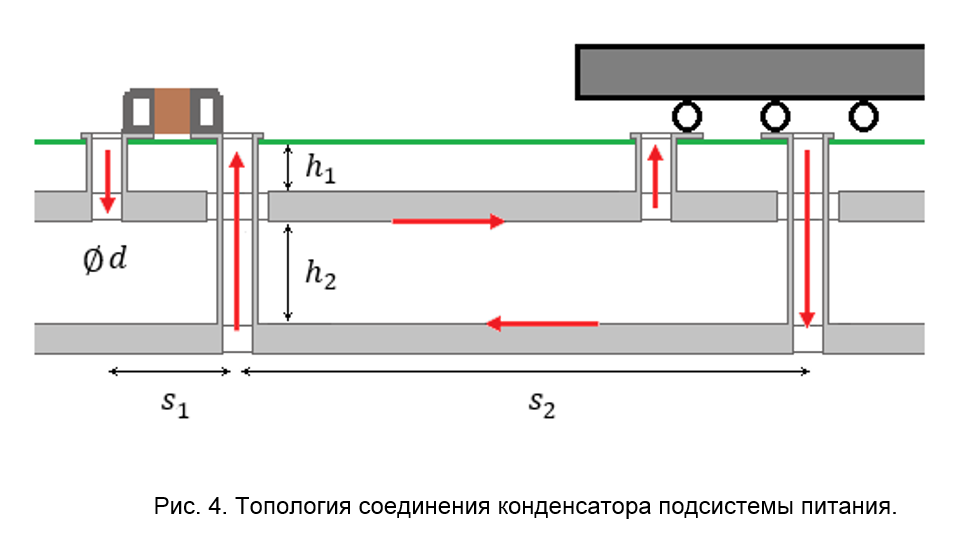

Using the mathematical apparatus of partial inductance of circuit sections and reduced approximate analytical formulas, it is possible to estimate the inductance of sections of the topology of a printed circuit board and vary their geometric parameters to reduce parasitic inductance. Consequently, reducing signal distortion, noise and EMI - issues that will be considered in subsequent articles of the cycle. It is also useful to make a calculation for the typical applied elements of the topology of the printed circuit board, so that later, when tracing, the estimated value of the parasitic inductance is associated with them. For example, Table 2 presents the values of the parasitic inductance of the elements of the topology of the connection of the capacitor of the power subsystem with different geometry parameters (Fig. 4).

Literature

[1] PCB Design Guidelines For Reduced EMI. Texas Instruments, 1999.

[2] Why You Should Be Cautious About EMC Design Rules. LearnEMC, 2017.

[3] Sivukhin D.V. General course of physics. T. III. Electricity. Ed. 4th M .: Fizmatlit, 2004.

[4] Bogatin E. What is Inductance? Printed Circuit Design & Manufacture, 2007.

[5] Bogatin E. Signal and power integrity - simplified. 2 nd ed. Pearson, 2004.

[6] Paul CR What Do We Mean By “Inductance”? Part I: Loop Inductance. IEEE Practical Papers, 2007.

[7] Paul CR Inductance: loop and partial. Wiley, 2010.

The article was first published in the magazine "Components and Technologies" 2017, №11. The publication on “Geektimes” is coordinated with the editors of the magazine.

Source: https://habr.com/ru/post/409873/